在CoPoS方面,中信投顧分析師張敦翔表示,今年上半年台積電與封測廠(OSAT)將導入首批機台進行測試,但目前仍屬測試階段,產出規模有限。市場雖普遍預期2028年放量,但實際觀察最快也要到明年下半年才有機會逐步放量,期間仍需歷經驗證、量產導入與設備穩定等階段,整體時程較預期拉長。

張敦翔指出,CoPoS具備放大晶片面積、提升單片晶圓切割效率的優勢,有助降低成本,對IC設計業者具吸引力,長期發展具必要性。

在產能布局上,供應鏈透露,目前龍潭廠(AP6)仍以測試線為主,今年第一季已陸續交機,未來若進入量產,仍需時間準備,且有機會轉往嘉義廠(AP7)後續產線擴充。

至於COUPE技術,張敦翔指出,目前仍在驗證階段,CPO設備尚未成熟,應用需時間醞釀,預期明年有機會開始放量,但規模難與GPU應用相比。

在面板級封裝領域,張敦翔形容目前為「百家爭鳴」,各家技術路線分歧,但核心趨勢仍在於透過放大尺寸提升單位產出、降低成本。台積電採用310x310毫米尺寸,接近12吋晶圓規格,在製程難度與成本間取得平衡,並優先鎖定AI應用。

更先進的SoIC技術也逐步進入量產階段。張敦翔指出,今年產能約1.5萬至2萬片,明年有望提升至4萬至5萬片,主要由AI客戶需求帶動,包括輝達新一代晶片與未來CPO應用。

技術上,SoIC採用Hybrid Bonding(混合鍵合),相較CoWoS透過微凸塊連接晶片,可直接銅對銅貼合,大幅提升I/O密度與電晶體整合能力,並減少空間浪費。該技術雖對對位精度要求高,但已發展多年,在客戶需求推動下正邁向商業化量產。

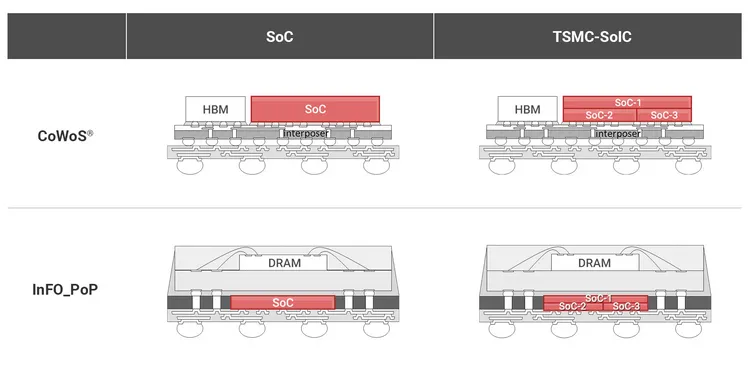

整體而言,台積電先進封裝布局涵蓋CoWoS、CoPoS、CPO與SoIC等多項技術,多數仍處於驗證或初期放量階段,但隨AI需求持續擴張,未來數年將逐步進入成長軌道。

此外,台積電技術論壇(TSMC 2026 Technology Symposium)也將於法說會後展開全球巡迴,4月22日自北美Santa Clara起跑,5月依序於新竹與阿姆斯特丹舉行,6月與7月則前進上海與橫濱。

論壇將聚焦HPC、智慧手機、物聯網與車用平台,並展示3奈米、2奈米、A16、A14等先進製程進展,以及3DFabric在SoIC、InFO、CoWoS與SoW等先進封裝技術成果,同時涵蓋低功耗、射頻、嵌入式記憶體與電源管理等技術突破,並強調產能擴充與綠色製造布局。

點擊閱讀下一則新聞

點擊閱讀下一則新聞