CoWoS產能三年翻三倍 AI算力競賽推升先進封裝需求

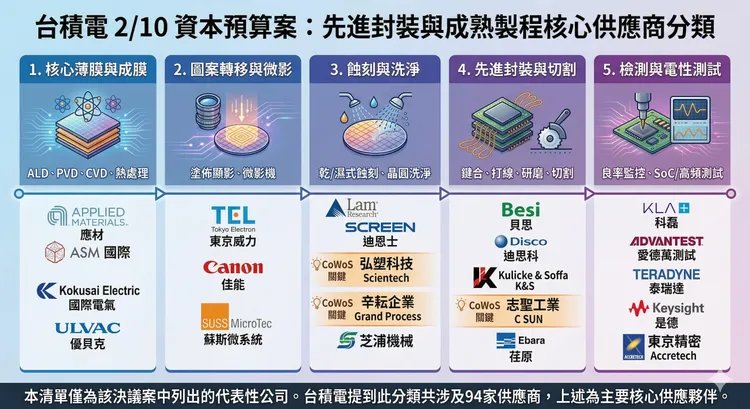

根據TrendForce分析,過去半導體設備投資中,約80%至90%集中於前段晶圓製造設備,封測設備投資比例相對較低。然而隨著電晶體微縮逐漸逼近物理極限,產業開始透過先進封裝與異質整合延續摩爾定律,使先進封裝設備需求快速成長。在AI與高效能運算帶動下,先進封裝相關設備需求增速甚至已超越部分前段製程設備。

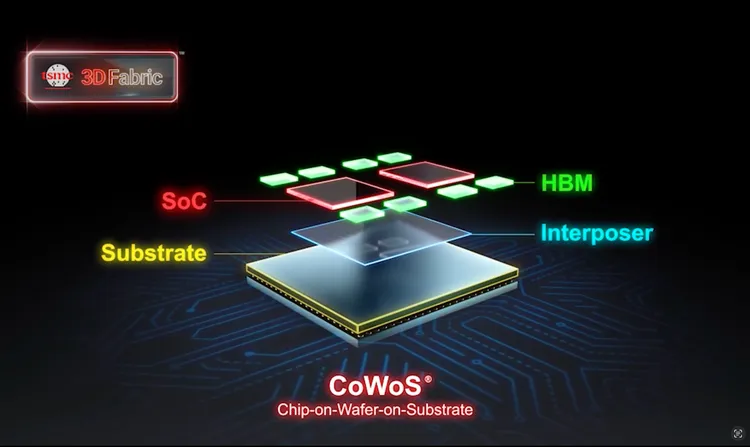

台積電在先進封裝領域已布局多年。公司於2020年推出3DFabric技術,並於2022年成立3DFabric聯盟,整合SoIC、CoWoS與InFO等技術,同時透過開放創新平台(OIP)串聯設計、IP、封裝與材料等合作夥伴,建立完整生態系,為3D堆疊與異質整合奠定基礎。

隨著AI晶片需求暴增,CoWoS(Chip-on-Wafer-on-Substrate)產能已成為全球半導體最稀缺資源之一。IDC資深研究經理曾冠瑋指出,台積電CoWoS擴產速度驚人,從2024年約33萬片、2025年65萬片,到2026年可望接近110萬片,但在大型模型與企業AI需求推動下仍可能不足。他直言,未來兩年CoWoS「一定不夠用」,產能缺口將成為AI供應鏈的關鍵瓶頸。

曾冠瑋表示,CoWoS需求主要來自GPU、AI ASIC與高階加速器的大量拉貨,尤其Google對CoWoS需求預計2026年成長約60%,顯示雲端服務商(CSP)正加速擴建AI訓練叢集。即使台積電持續擴產,NVIDIA、Google、AWS與Microsoft等科技巨頭同步搶產能,使整體供給長期維持緊繃。

半導體群山01|AI掀史上最大擴廠潮!台積電560億資本支出流向曝光 設備霸權浮現

半導體群山02|神山外溢效應發酵!台積電帶動本土供應鏈 在地廠商尋求突破

半導體群山04|建廠進度成關鍵瓶頸 台灣廠務國家隊從單打獨鬥走向團體戰模式

法人研究報告指出,由於AI晶片需求增速遠超產能擴充幅度,台積電可能進一步調整先進封裝產能規畫。供應鏈調查顯示,台積電可能將AP7廠二期原本規畫擴充SoIC產能的部分空間,轉而用於擴大CoWoS產線,使2027年底CoWoS月產能預估上調至17萬片。

目前CoWoS製程中,台積電多負責前段的CoW製程,而後段的WoS環節則有部分外包給封測廠(OSAT)處理。隨著需求持續升溫,日月光、京元電與Amkor等業者也逐步參與相關封裝環節,成為AI供應鏈的重要補充力量。

先進封裝供應鏈成形 台廠逐步卡位關鍵環節

與前段製程設備高度標準化不同,先進封裝產線需頻繁調整製程參數,設備往往需要高度客製化並具備快速技術支援能力。相較於前段設備市場已由少數國際大廠寡占,封裝設備領域尚未形成明顯壟斷格局,使具備在地服務能力與製程整合經驗的台灣設備商更容易切入供應鏈。

在CoWoS製程中,濕製程設備扮演關鍵角色,涵蓋清洗、蝕刻與去阻劑等環節。尤其在HBM堆疊過程中,晶片表面處理的潔淨度直接影響良率,一旦微粒控制失敗,可能導致整體模組報廢,使高精度清洗技術成為隱形門檻。台廠如弘塑與辛耘,憑藉過去在先進封裝與InFO製程累積的技術經驗,成功卡位關鍵供應鏈。由於設備需與製程高度協同優化,在地供應商能提供更快的調整速度與即時服務,也讓台積電更傾向優先導入本土設備。

部分台廠也在封裝製程與散熱設備領域逐步站穩腳步,例如製程解決方案廠印能科技近年受惠先進封裝需求成長。隨Chiplet異質整合與大尺寸封裝成為主流,氣泡與助焊劑殘留逐漸成為影響良率的重要問題。印能的產品透過氣流與熱能控制技術去除氣泡與殘留物並提升製程可靠度,目前已切入多家大廠先進封裝製程,並逐步延伸至面板級扇出型封裝(FOPLP)領域。

在封裝製程與散熱設備方面,竑騰科技近年亦受惠AI與高效能運算(HPC)需求快速成長。公司表示,透過植片、點膠、壓合與AOI檢測等設備技術的持續研發,已成功切入AI與GPU等先進封裝市場。隨著AI晶片封裝密度與功耗持續提升,散熱需求同步升溫,竑騰也強化熱介面材料(TIM)製程設備布局,包括微膠量點膠、導熱膏塗佈與銦片貼合等技術,協助封測廠提升散熱效率與製程穩定度。

隨著先進封裝需求持續升溫,設備需求也逐步延伸至檢測與量測領域,隨著封裝技術朝3D堆疊與大型封裝發展,製程複雜度提升,也讓設備協同開發與在地服務能力的重要性持續提高。

先進封裝擴散至供應鏈 2027投資焦點浮現

相較於CoWoS的高速擴產,下一波先進封裝技術正逐步浮現,包括SoIC、CoPoS與混合鍵合(Hybrid Bonding)等方案。其中,SoIC與混合鍵合強調晶片間直接鍵合與極致對位精度,技術門檻幾乎逼近前段製程,也使封裝與晶圓製造的界線逐漸模糊。CoPoS(Chip-on-Panel-on-Substrate)則被視為延伸CoWoS產能的重要方向,透過更大尺寸基板提升封裝效率,市場傳出今年將啟動試產,明年可望進入量產。

隨著先進封裝競爭升溫,產業戰線也逐漸延伸至材料與耗材供應鏈。例如德鑫大聯盟成員頌勝,長期深耕化學機械研磨(CMP)耗材市場,產品廣泛應用於晶圓代工、記憶體與先進封裝製程。

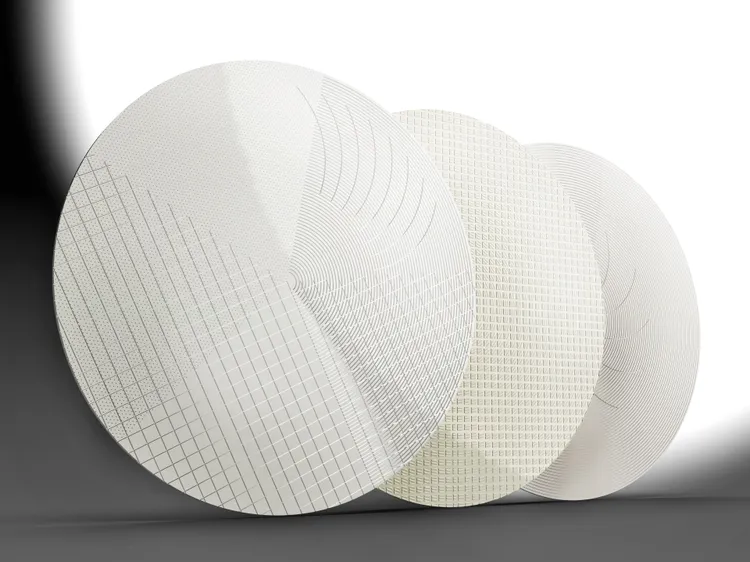

在製程持續微縮下,CMP需求快速提升。過去單一晶片僅需十餘次研磨,但以台積電FinFET晶片為例,已需超過10種材料、約30次CMP研磨;2奈米製程需求更可能達成熟製程的3至5倍,A16製程CMP層數甚至達77道。CMP負責確保晶圓表面平整並精準控制材料去除,直接影響製程精度與結構可靠度,也帶動研磨墊等耗材需求同步成長。

此外,TSV、扇出型封裝(Fan-Out)、2.5D矽中介層與3D IC等技術,對表面平整度與結構精度要求更高;隨著晶背供電(BSPD)導入,對晶圓厚度控制更加嚴格,也進一步推升CMP需求,成為耗材市場的重要成長動能。

為降低供應風險,台積電近年積極推動封裝關鍵化學品在地化生產,例如電鍍添加劑導入在地製造後,生產週期由約60天縮短至20天,並逐步導入先進封裝產線。隨著封裝技術走向高度整合,材料與設備的協同開發能力,正成為產業競爭的重要關鍵。

同時,由於部分先進材料具高風險與運輸限制,無法空運而需仰賴海運,短鏈供應與在地化生產的重要性顯著提升。當封裝技術進入高度系統化階段,能否建立快速反應的在地供應網絡,已成為影響競爭力的關鍵因素。

外資也開始聚焦先進封裝供應鏈。瑞銀投資銀行台灣研究主管艾藍迪(Randy Abrams)指出,研究焦點已從晶圓代工延伸至測試與封裝,台灣廠商逐步浮上檯面。瑞銀分析師林莉鈞也表示,先進封裝技術歷經十多年醞釀才進入量產,國際大廠早期投入有限,反而讓台灣供應鏈取得切入契機。

她進一步指出,台灣在設備如膠機、AOI與曝光機,以及耗材如鑽石刀具與部分材料領域,已有廠商展現競爭力。未來除CoWoS外,先進封裝將延伸至晶圓級封裝(WLP)、多晶片模組(MCM)、3D堆疊與面板級封裝(FOPLP)等領域,2027年後可望迎來下一波投資週期。

資本市場資金流向也反映相同趨勢。根據安永統計,截至2025年底,台灣上市市場籌資金額達845億元,其中半導體業占比逾四成;其中設備廠鴻勁籌資344.69億元,占整體上市籌資額約40.77%。另一方面,上櫃市場籌資205億元中,半導體業亦占近五成,新應材與印能科技合計占比逾四成,顯示資金正持續流向半導體材料與設備供應鏈。

先進封裝改寫半導體戰局 台灣設備國家隊撐起群山

隨著先進封裝產能逐漸成為AI晶片產出的關鍵瓶頸,半導體產業競爭重心也隨之轉移。過去由前段製程設備主導的技術高門檻,正逐步向封裝與系統整合延伸。對台灣廠商而言,憑藉長期累積的製程整合經驗與在地服務能力,設備商得以在這場封裝革命中找到新的突破口。當封裝技術逐漸成為影響晶片效能與功耗的關鍵環節,相關設備需求也同步增加,使具備精密製造與快速技術支援能力的台灣設備廠迎來新的成長機會。

從弘塑、辛耘、萬潤到志聖,這些過去多半扮演在地供應角色的設備廠商,如今正逐步站上先進封裝供應鏈的重要位置。對台灣半導體產業而言,這片曾被視為後段製程的領域,正逐漸轉化為新的技術戰場。

不過,隨著先進封裝需求快速升溫,國際半導體設備大廠也開始嗅到商機。艾司摩爾(ASML)指出,一顆高階晶片約需70至100道微影程序,其中僅十多層使用EUV,其餘仍仰賴DUV設備。隨著矽中介層尺寸持續放大,「越大越難做」成為新的製程挑戰。ASML推出I-line系統(XT:260),具備更大曝光場與翹曲補償能力,正式切入先進後段封裝領域。

應用材料(Applied Materials)集團副總裁暨台灣區總裁余定陸也表示,隨著Chiplet架構逐漸成為主流,封裝技術的重要性持續提升。他指出,當晶片進入封裝階段時,前段製程已投入大量成本,一旦封裝失敗損失可能如同一台車,因此對製程可靠度與設備精度的要求也同步提高。

隨著國際設備大廠加速布局,先進封裝設備競爭正逐步走向全球化。對台灣設備廠商而言,先進封裝既是新一輪產業升級的機會,也意味著未來將面對更激烈的技術與市場競爭。

點擊閱讀下一則新聞

點擊閱讀下一則新聞