隨著AI晶片進入2奈米及更先進節點,電晶體架構、材料與製程控制的挑戰同步提高。為因應環繞式閘極(Gate-All-Around, GAA)電晶體與新一代記憶體技術需求,應材近期推出三項材料工程系統,分別針對通道表面處理、深溝槽蝕刻與金屬接點材料三項關鍵製程問題提供解決方案。

這三大系統包括Producer Viva自由基處理系統、Centris Sym3 Z Magnum蝕刻系統,以及Centris Spectral鉬原子層沉積系統。目前相關設備已獲多家晶圓代工與邏輯晶片製造商採用,預期將在下一代AI晶片效能與能源效率提升上扮演重要角色。

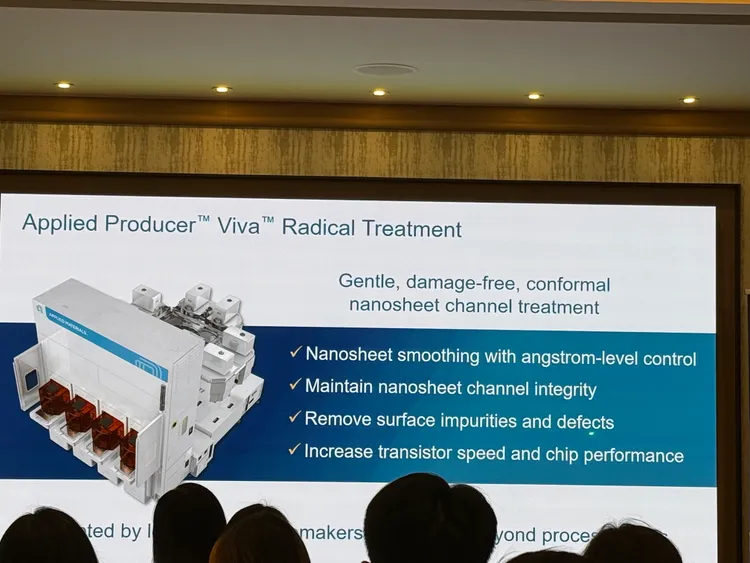

Producer Viva自由基處理系統:提升奈米片通道品質

應用材料處長許君瑜指出,隨著AI資料中心規模持續擴大,預估到2030年AI資料中心電力消耗可能占全球約10%,提升晶片能源效率已成為產業重要課題。

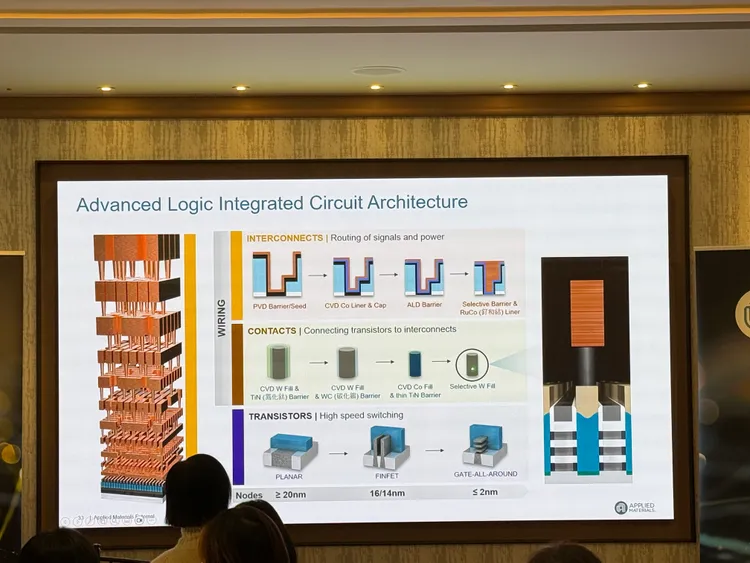

在電晶體架構上,產業正從FinFET轉向GAA設計,透過閘極完整包覆通道,可讓電晶體在較低電壓下運作,有助於降低功耗並提升效率,但3D結構也讓製程複雜度大幅增加,一顆晶片可能需要超過2000道製程步驟。

在GAA架構,核心元件為水平堆疊的矽奈米片,其厚度僅數奈米。由於電子主要在奈米片表面移動,若表面存在微小粗糙或雜質,可能造成電子散射,影響電晶體效能。

為改善此問題,應材推出Producer Viva自由基處理系統。該系統透過遠端電漿產生中性自由基,在過程中過濾高能離子,使表面處理更加溫和且可精準控制,能在不破壞奈米片結構的情況下改善表面品質。

透過高精度氣體分布設計,系統可在整片晶圓上均勻作用,即使在複雜的3D電晶體結構中也能維持一致性。許君瑜表示,由於奈米片厚度僅約3至4奈米,製程控制必須達到原子級精度,而Viva技術能在不損傷結構的情況下改善表面品質,提升通道導電能力與晶片效能。

目前該系統已導入2奈米及以下先進製程節點,也可延伸應用於低介電材料處理、銅佈線改善與影像感測器製程等領域。

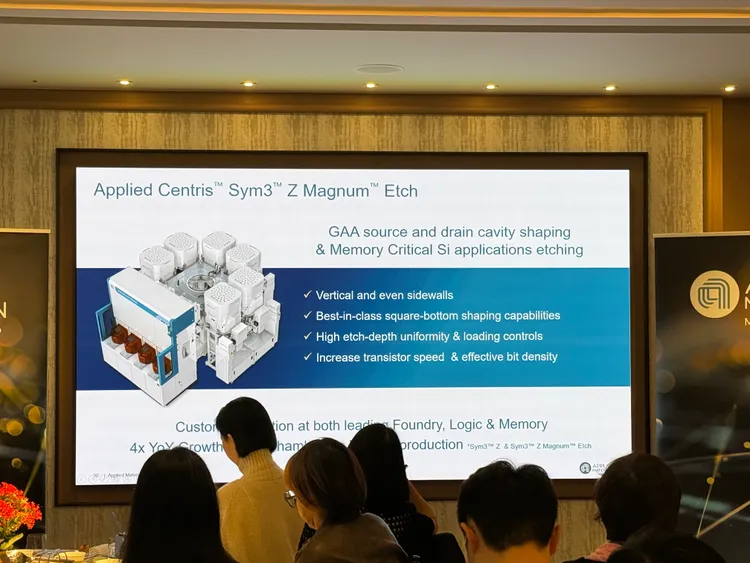

Centris Sym3 Z Magnum蝕刻系統:打造精準3D結構

在GAA製造過程中,Source/Drain區域的蝕刻製程直接影響電晶體性能與晶片效能。應用材料資深處長劉中偉表示,隨著晶片結構日益立體化,蝕刻製程精準度與一致性變得更加重要。

在GAA架構下,晶片需要形成深而狹窄的溝槽結構。由於溝槽深寬比高且間距縮小,蝕刻過程容易受到側壁遮蔽效應影響,導致蝕刻不均勻。此外,Source/Drain區域同時包含不同材料,若控制不佳,可能影響後續元件性能。

為解決此問題,應材在既有Sym3 Z蝕刻平台上推出升級版Sym3 Z Magnum系統。該設備透過脈衝電壓技術(PVT),能精準控制電漿離子的能量與方向,使蝕刻過程更加穩定。

在最新系統中,應材進一步導入第二代脈衝電壓技術(PVT2),並整合射頻與直流偏壓控制,使離子在進入溝槽時能維持適當角度與能量。這項技術可在保持筆直側壁的同時,形成平坦的溝槽底部,提升結構一致性。

劉中偉指出,若溝槽底部形狀不平整,可能影響後續磊晶成長與通道性能。透過新的離子控制技術,Sym3 Z Magnum能蝕刻出更均勻的3D結構,為後續製程提供更穩定基礎。

除了先進邏輯製程外,該系統也可應用於DRAM與高頻寬記憶體(HBM)製造,協助打造更高密度記憶體結構。目前Sym3 Z系列設備在全球已部署超過250套製程系統,並被多家晶片製造商採用。

Centris Spectral ALD系統:降低接點電阻

隨著製程持續微縮至2奈米以下,晶片內部金屬接點的電阻問題逐漸成為限制效能的重要因素。為解決此挑戰,應材推出Centris Spectral原子層沉積(ALD)系統,導入單晶鉬(Molybdenum)材料作為新一代接點金屬,協助晶片製造商提升運算速度與能源效率。

應用材料資深處長吳峯岳指出,在現代邏輯晶片架構中,電路大致可分為三個部分:最底層是電晶體(Transistor),負責進行訊號開關與運算;上層則是銅佈線(Interconnect),負責傳輸電力與訊號;而位於兩者之間的金屬接點(Contact)則負責將電晶體與佈線網路連接起來,確保電流與訊號能順利傳遞。隨著製程節點不斷縮小,接點尺寸也隨之縮小,使材料導電能力逐漸成為影響晶片效能與功耗的重要因素。

目前業界普遍使用鎢(Tungsten)作為接點金屬,但當結構縮小至奈米尺度後,鎢材料的導電能力逐漸受到限制,接點電阻持續上升,進而影響訊號傳輸效率與晶片整體性能。吳峯岳表示,一顆先進晶片內往往包含數十億個金屬接點,若每個接點的電阻略微增加,累積後將對晶片速度與功耗造成明顯影響,因此如何降低接點電阻已成為先進製程的重要課題。

為突破此限制,應材開發Centris Spectral Moly ALD系統,採用單晶鉬作為新一代接點材料。鉬在極薄結構下仍能維持良好的電子傳導能力,可有效降低接點電阻。根據應材資料,與目前業界使用的選擇性鎢技術相比,鉬接點可將關鍵接點電阻降低約15%。由於晶片內部存在大量接點,這些微小的改善在整體系統層級上可轉化為顯著的效能提升與能源效率改善,對AI晶片等高效能運算應用尤為重要。

Spectral系統採用原子層沉積(ALD)技術,可在原子尺度下精準沉積金屬薄膜,並透過多反應器架構設計與精密化學供給系統,使材料沉積過程更穩定且可控,有助於確保製程一致性與良率。

應材表示,目前Centris Spectral Moly系統已導入2奈米及更先進製程節點,隨著AI與高效能運算需求持續提升,降低接點電阻並提升晶片能源效率,將成為下一世代半導體技術發展的重要方向。

點擊閱讀下一則新聞

點擊閱讀下一則新聞