AI用電推動製程微縮 半導體市場邁向兆美元規模

徐寬成表示,從 PC、網路到智慧手機,各代運算浪潮都推升半導體產值,如今 AI 讓增長曲線再度抬升。全球半導體市場目前約 6,000 億美元,市場預估到 2030 年將突破 1 兆美元,甚至上看 1.6 兆美元,其中,高效能運算(HPC)可能占比高達四成,成為推動半導體的主要動能。

他強調,AI 的成長並非僅侷限在先進製程,而是帶動所有製程、所有類別全面升溫,包括先進邏輯晶片、HBM 記憶體、車用與工控晶片、感測器與電源管理 IC,都因 AI 的資料洪流與算力需求而同步成長。ASML 的產品線橫跨 EUV、DUV 到 I-line,在 AI 時代扮演支撐整體半導體製造的基礎建設角色。

徐寬成提醒,當前大型 AI 資料中心的單點電力規模動輒以 Gigawatt 計,一座 1GW 伺服器園區等同一座核電廠。若全球 AI 用電在五年內達到 50~140GW,是極為驚人的數字。因此,先進製程每代功耗改善,即便實際落地僅兩成,也足以在 GW 等級產生巨大差異。且節點代代疊加後,節能效果將進一步放大。他強調,若不持續推進製程微縮,AI 的算力需求將使全球電力在短時間內面臨更嚴峻壓力。

摩爾定律仍在延伸 High-NA EUV 驅動下一個十年微縮藍圖

徐寬成強調,外界認為摩爾定律走到盡頭的說法並不正確,更多反映的是技術追不上 AI 爆炸性需求,而非微縮停止。他指出,依產業路線圖,N2 之後 FinFET 將由 GAA 取代,並可延續至少三個世代,接續則是上下堆疊的 3D 電晶體架構,如 CFET。這些新技術意味著未來 10~15 年製程仍會沿著摩爾定律推進,每一代節點約可帶來 20%~30% 的能耗改善。在 AI 用電飆升、資料中心動輒以 Gigawatt 計算的時代,微縮不僅沒有終止,反而變得比過去更為關鍵。

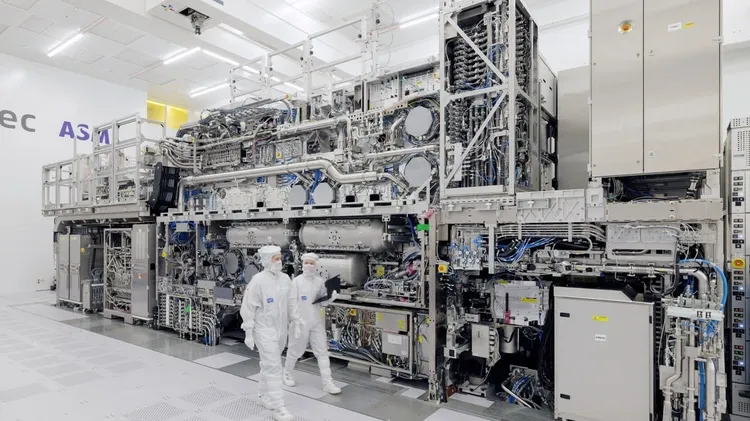

在設備端,他說明目前先進製程仍依賴 0.33 NA 的 Low-NA EUV,ASML 近年持續提升平台的可用性與生產效率,預期五年內可為客戶降低約三成曝光成本。下一代 0.55 NA 的 High-NA EUV 則已由 EXE:5200 在今年第二季交付客戶,截至九月已累計完成超過 35 萬片晶圓曝光。High-NA 的優勢在於可用一次曝光取代過去三次曝光流程,在 2D 複雜圖形上具顯著解析與精度優勢,能同步縮短製程時間並降低每片晶圓成本,晶圓代工等大客戶皆已公開證實採用。

先進封裝推升 I-line 回歸舞台 Holistic Lithography 成關鍵技術

徐寬成補充,一顆高階晶片約需 70 至 100 道微影程序,其中僅十多層使用 EUV,其餘仍倚賴 DUV。ASML 最新浸潤式設備(NXT:2150i )每小時可處理逾 300 片晶圓,而 KrF平台(NXT:870B)因涵蓋大量成熟製程投片,仍具關鍵地位。隨先進封裝需求大幅提升、矽中介層尺寸放大,「越大越難做」成為新挑戰。

ASML 推出最新I-line系統(XT:260)則是放大曝光場並具翹曲補償能力,正式跨入 先進後段封裝領域,也讓過去較被忽略的 I-line 再度受到重視。徐寬成也透露,目前已經出貨1台,目前待客戶驗證。

為因應日益嚴格的線寬與疊對精度(Overlay)要求,ASML 推出「全方位微影技術(Holistic Lithography)」概念,將曝光、量測、檢測與運算式微影整合成資料回饋迴圈,使可控參數提升至原先的數萬倍,Overlay 極限可再降低數個量級,對 3D 堆疊與 wafer bonding 尤其重要。在檢測端,ASML 旗下 HMI 電子束設備從 25 束 eScan 1100 進化至超過 2,000 束的 eScan 2200,大幅提升生產效率。

徐寬成強調,半導體製程推進從來不是單一設備廠就能完成,而是整個生態系協作,從 EUV、High-NA、DUV、封裝到檢測與材料全面進化,才能支撐 AI 時代的爆發性算力需求與能源壓力。

點擊閱讀下一則新聞

點擊閱讀下一則新聞